|

PowerDC 2017新功能

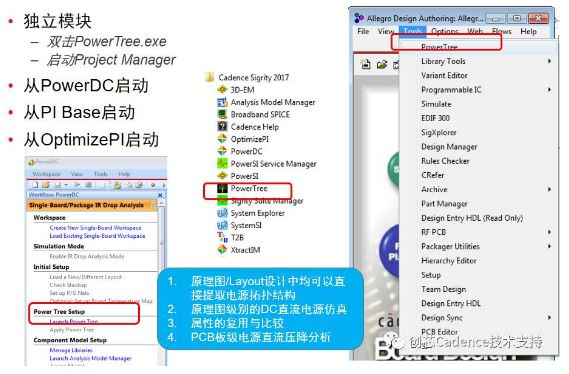

IntegratedPowerTree and PowerDC

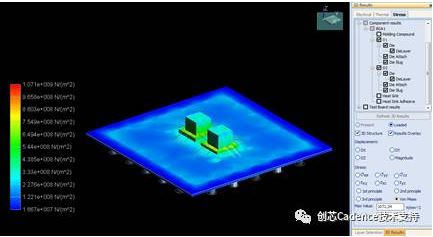

Thermal Stress

• 热仿真结果的保存/加载功能得到加强

– XML格式数据–2D分布图

– 3D形变图

• Via/Bump/Ball/Wire/Leadframe的完整3D仿真结果

Miscellaneous Enhancements

• 支持TCL命令

|

sigrity::import stackup{C:\Users\jackien\Desktop\Stackup.csv}

sigrity::update option–AutoExportDist2Txt {0|1}

sigrity::update option -ByPassYesNoCancel{0|1|2|3} {!}

sigrity::update mat|material {file name}-MatName {material name} | -all

|

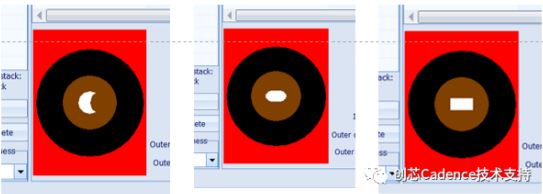

• PowerDC仿真支持polygon/oblong/rectangle等形状过孔

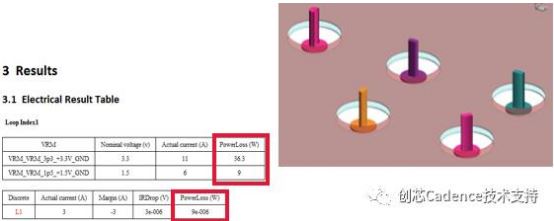

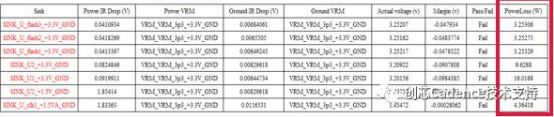

• sink/VRM/discrete功率损耗报告

• 支持多线程计算功率损耗、电流等结果

OptimizePI 2017新功能

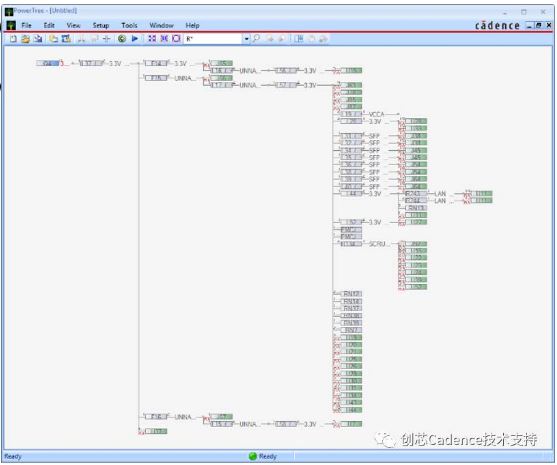

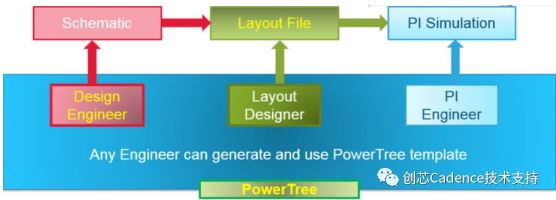

PowerTree与OptimizePI集成仿真优化环境

• PowerTree基于团队设计的PDN仿真报告

– PowerTree在原理图阶段分析IR-Drop压降

– 器件模型在早期即可得到验证

– Layout设计前的PDN分析

– 仿真优化周期内的数据复用

– DC/AC仿真参数自动设置

AMM/PowerTree/OptimizePI支持目标阻抗规则

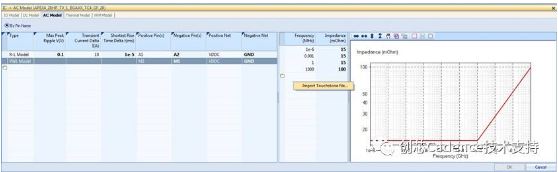

• PowerTree可以在任何器件上设置目标阻抗规则

– 所有器件均可以基于目标阻抗规则进行自动检查,快速确定PDN性能是否符合设计要求

• 支持两种不同类型的目标阻抗设置

– R-L模型:纹波峰值、最大电流变化量、上升时间变化量

– PWL模型:阻抗值离散分布、单端口S参数模型

PDN阻抗检查流程更新(一)

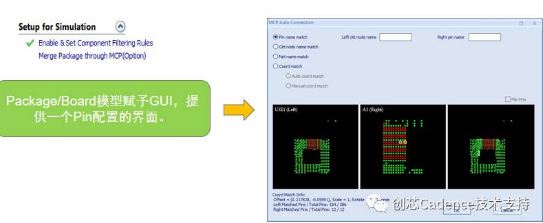

• 全新的GUI,帮助工程师轻松完成PCB上IC封装模型赋予

PDN阻抗检查流程更新(二)

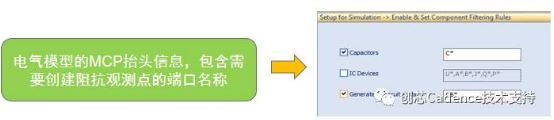

• 基于MCP协议的IC封装模型,自动创建子电路阻抗观测点

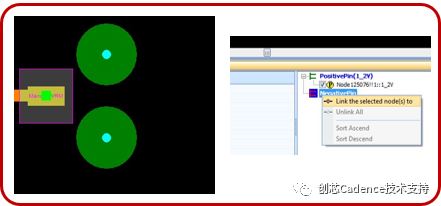

• 创建VRM模型与阻抗观测点的工作模式下,新版本支持“Linkselected nodes to”功能

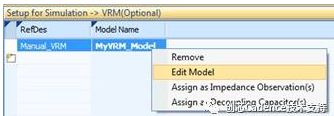

• Workflow流程中支持右键直接编辑VRM模型

PDN阻抗检查流程更新(三)

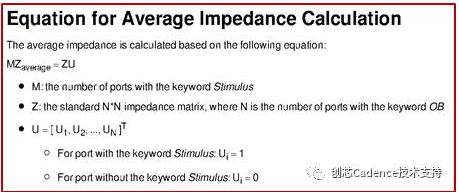

• 全新的 “average”阻抗计算方法,用于解决一些专用名称定义的模型

– “Stimulus”目前在阻抗观测点设置中,即为关键词

– 当Sigrity判断到这类关键词,“average”阻抗将在这些阻抗观测点计算出来

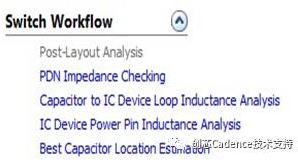

最佳电容位置评估支持Workflow切换

• OptimizePI技术让工程师能够无缝地完成不同仿真流程的切换

• OptimizePI能够将仿真参数设置继承到其它仿真流程,其它仿真不需要额外设置或只需要一点设置,即可开始仿真

• “BestCapacitor Location Estimation” (BCLE)仿真流程支持这种流程切换

• BCLE仿真流程主要应用在PDN性能无法满足目标阻抗要求之后

SPEED2000新功能

New ESD Simulation Workflow

• Electrostatic discharge (ESD)防静电分析

–人体带电对手机的影响

–Cable线缆带电对USB端子的影响

• ESD危害分析

–完整的器件、系统的损坏

–不可预测的器件、系统运行状态

–EMI问题

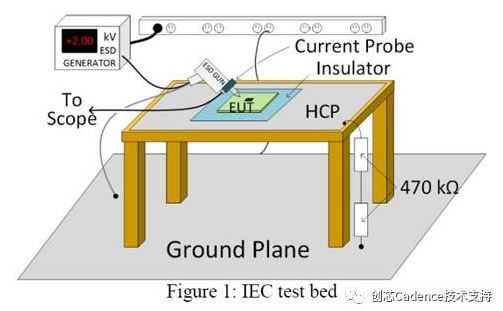

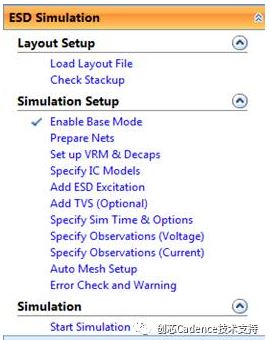

ESD Simulation Workflow in Sigrity 2017 Portfolio

• ESD仿真流程提供GUI,帮助工程师轻松进行仿真设置,无论是PCB或者Package封装

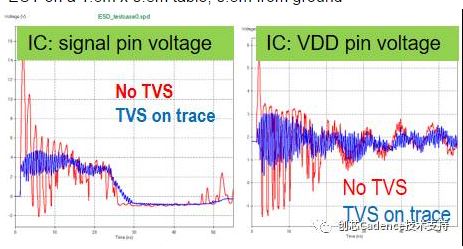

• ESD gun charges to up to 8kV, then discharge into equipment under test (EUT)

• EUT on a 1.6m x 0.8m table, 0.8m from ground

Allegro Database Support

• 支持背钻孔结构

- 当.brd文件转换为.spd仿真文件时,背钻孔结构模型将转换并用于仿真

• 支持tabbed布线

-Tab布线的网络,可以直接转换到.spd仿真文件,并进行Tabbed结构的布线仿真

Sigrity 2017是Cadence系统设计使能的重要技术,从芯片、电路板、到全系统,助企业打造创新的高质量电子产品。

如需了解有关Sigrity 2017系列产品的更多内容 。可以通过e-news@u-c.com.cn来索取,或致电技术服务热线4007-188-616与我们联系。

|