高速串行和并行链路时域仿真验证

完全自动化的芯片到芯片级信号完整性分析验证工具,包含针对并行总线和串行接口分析的两大模块。

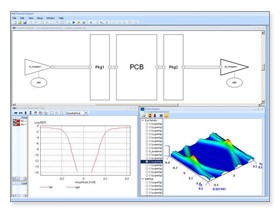

Sigrity™ SystemSI™ 利用完整的芯片到芯片级信号完整性(SI)分析验证手段解决当前高速设计中面临的各种挑战。SystemSI包含两大模块,System-Paralel Bus Analysis专用于并行总线分析, 而SystemSI-Serial Link Analysis则专注于SerDes通道的分析验证。

SystemSI 基于模块化的结构搭建系统拓扑,简单易用。随着设计的进行,用户可以将包含更多细节信息的精确模型加载到系统链路中作精确的验证分析。SystemSI支持频域分析、时域分析和统计分析三种分析手段,帮助用户验证并行和串行链路的系统性能是否满足设计指标

主要功能

SystemSI Parallel Bus Analysis

SystemSI Parallel Bus Analysis是专门针对源同步高速并行总线接口(如DDRx)而开发的系统级芯片到芯片验证工具。SystemSI-PBA的前仿真能力(包括3D全波Via-wizard建模能力)确保精确的宽带模型能够快速产生并与其他系统模块连接。而后仿真能力允许用户加入优化的、包含更多细节信息的实际版图模型并进行最终的验证分析。所有的SI效应如导体/介质损耗、反射、ISI码间干扰、串扰以及同步翻转噪声(SSN)等都能在一个仿真引擎中同步考虑。其非理想电源仿真能力能精确模拟真实PDN噪声对信号的干扰。强大的图形化编辑以及结果后处理能力使工程师能快速分析并优化系统设计。

SystemSI Serial Link Analysis

SystemSI Serial Link Analysis是专用于高速SerDes接口(如PCI-e, HDMI, SFP+, XAUI, Infiniband, SAS, SATA, USB等)进行系统级芯片到芯片验证的仿真工具。它允许用户基于简单的系统模板快速搭建仿真拓扑,易用性高。SystemSI-SLA支持工业标准的IBIS-AMI算法模型以及不同IC厂家提供的专用算法模型(VMI)。系统链路的不同模型如封装、连接器、PCB板、子卡等都能快速加载到系统链路中从而保证仿真具有从芯片到芯片的仿真精度。强大的链路仿真能力能完全仿真系统串扰、电源噪声等电路影响以及数据时钟恢复(CDR)、判决反馈(DFE)等算法模型对链路性能的影响。而高效的通道仿真也能根据数以百万位的通道激励和响应波形确定系统的误码率(BER)水平并验证抖动和噪声是否满足给定的设计裕量。

优势与特点

• 支持直流(DC)到10G以上串行链路模型的快速精确仿真

• 精确仿真非理想(Non-ideal)电源分配网络(PDN)与信号之间相互影响,尤其是同步翻转噪声(SSN)

• 简单易用的模块化系统拓扑编辑方式和新颖的基于网络的模块连接,直观清晰,易学易用;

• 强大的S参数处理能力,保证系统级时域仿真的精度和可靠性;

• 与其他Cadence® 工具如S参数模型提取、模型校准、等效SPICE电路模型转换、MCP模型连接等无缝连接,大大简化了仿真设置;

• 丰富的SPICE子电路模型支持,如常见的IBIS模型、Hspice网表、Touchstone、BNP、MCP电路等

• 完全自动化的、可定制的时域波形/眼图测试和报表打印功能

|