随着集成化程度的提高,印制板设计中FPGA引脚数量越来越多,设计难度越来越大,Cadence Allegro FPGA设计平台正是为了应对如此挑战才应运而生。它从创建初始引脚配置着手,紧密结合原理图工具,以共同确保复杂PCB布线顺畅。Cadence Allegro FPGA系统设计平台提供了一套完整的、可扩展的FPGA-PCB协同式设计解决方案,用于板级FPGA设计,它能够自动对引脚配置进行“芯片-规则-算法”的综合优化。Cadence

Allegro FPGA取代了易出错的手动引脚配置方式,以独特的自动布局解决方案,减少不必要的设计迭代,节省创建最优化引脚配置方案的时间,从而提高设计效率。

FPGA-PCB

协同设计解决方案

结合现在的FPGA产品特点,以及PCB上不同的引脚配置规则和用户自定义引脚,导致这种复杂设计过程非常耗时,延长了设计周期,增加了设计成本。

通常情况下,FPGA在手工进行pin-by-pin级的引脚调整时无法考虑PCB板中其他关键元器件(与FPGA相连元件)的布局,因此,手工完成pin-by-pin级布局后,往往会发现FPGA的引脚连接与PCB布局布线匹配得不尽人意。因此,如果不考虑PCB布局布线的影响,会给FPGA设计带来两个负面影响:一是由于引脚配置的不完善,导致PCB板的层数增加;二是需要反复进行不必要的迭代设计,延长了设计周期,而且这些不必要的迭代容易出错,更可能导致PCB的重新设计。

此外,手工进行多个FPGA的总体引脚配置,需要更多的时间来完成,设计者在此过程中,总需要在FPGA器件的可用性和FPGA子系统的设备成本之间做好权衡。

Cadence

Allegro FPGA System Planner提供了一个完整的、可扩展的FPGA-PCB协同设计解决方案,用户可以用它创建设计最佳的引脚配置方案。它能够根据用户产品定义、接口连接、引脚配置规则(FPGA-rules)以及FPGA在PCB板上的实际布局,来进行FPGA引脚配置的综合优化。

通过自动综合优化引脚配置,用户不仅减少了FPGA布局的初始引脚配置时间,还能够避免设计错误的发生。这种独特的引脚配置方案,消除了手工设计方法中固有的不必要的物理设计迭代。

Allegro

FPGA System Planner集成了Design Entry CIS, Design Entry HDL和Allegro

PCB Editor等PCB设计模块,可以直接读取和创建Capture/HDL原理图和符号文件,其Floorplan 窗口可直接读取Allegro PCB Editor的封装库。如果PCB板级设计需要调整布局,用户可以直接在Allegro PCB Editor环境下调用Allegro FPGA System

Planner来优化引脚配置。

优点

l 可扩展、高性价比的FPGA-PCB协同设计解决方案

l 加速PCB设计流程,能够用最短的时间优化引脚配置

l 加速FPGA与PCB之间的设计集成

l 减少由于FPGA引脚配置不当引起的反复设计迭代

l 通过优化引脚配置,优化PCB设计,减少设计层数

l 减少PCB板层设计进程中不必要的设计迭代

功能特性

Allegro FSP设计技术

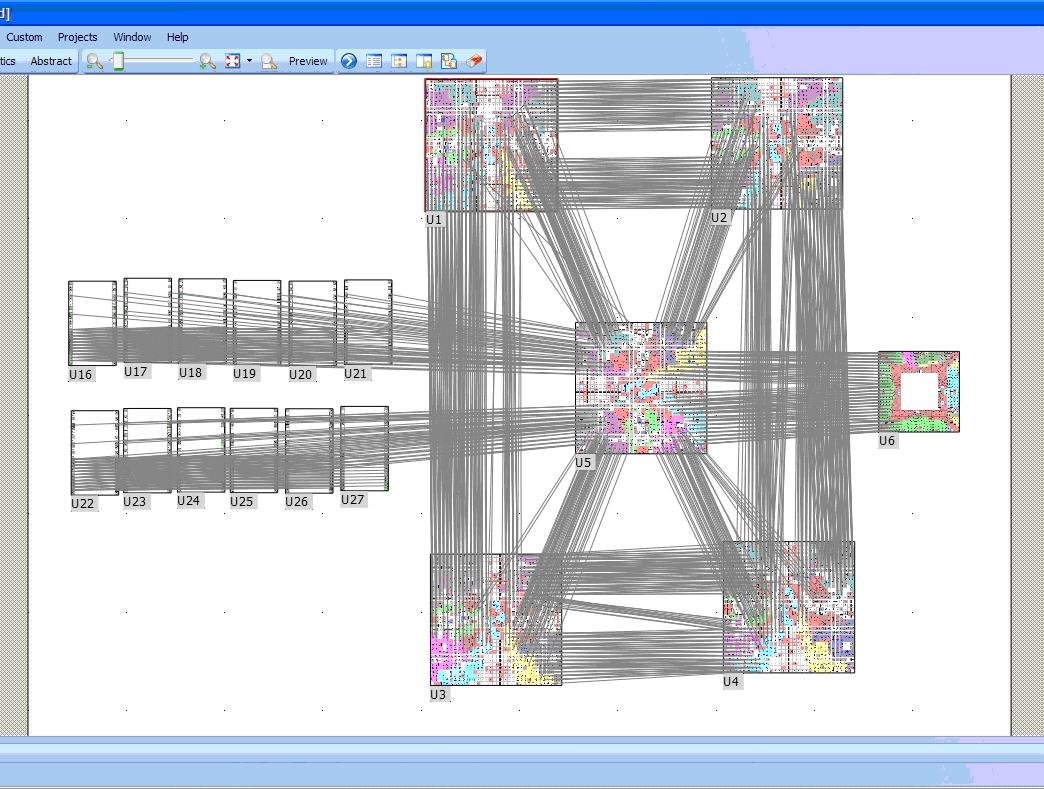

Allegro FSP系统是Cadence

PCB设计中的一个子系统,包括一个或多个与FPGA相连的FPGA和非FPGA元件。

传统的引脚配置方法是典型的手工引脚调整方法,这通常都是基于一个表格进行调整的。这些传统的手工配置方式,使得用户在进行引脚配置时,不能够考虑其它元件布局,以及接口、信号的布线性能。

更重要的是,这些设计工具没有在线实时规则检查功能,用户不能确保信号被正确配置给FPGA引脚。这样设计的结果就是,用户必须在这些基于表格的设计工具与FPGA生产商支持的设计工具之间作若干次迭代设计后,才能找到合适的引脚配置。

这种方式导致PCB板层设计师和FPGA设计师之间可能出现大量的设计迭代,因为前者不能在可用的PCB板层对FPGA进行准确的信号布线,而后者不得不接受PCB板层设计师纸面和口头上建议来进行引脚配置。这样的情况下,一旦FPGA设计师修改引脚配置,那么所有的硬件设计师都必须修改原理图设计,才能进行下一步的PCB重新设计,如此反复的设计迭代增加了许多工作量,会降低团队成员的工作积极性。

此外,由于这是一项手工配置进程,设计中的错误很难被发现,这可能导致首次物理设计的失败,增加设计迭代,不能实现设计即正确的理念。

虽然这些手工配置工具可以自动综合各方面的修改,包括FPGA设计师、硬件设计师、PCB板层设计师的设计修改,但是它们并不能解决这些设计迭代的根源问题。因为引脚配置不仅由以下三点决定――FPGA资源可用性、FPGA生产商的引脚配置规则和印制电路板FPGA引脚布线性能,手工配置还需要在设计末端进行许多迭代,从而延迟了如今复杂的、拥有多个多引脚FPGA印制板的设计周期,增加了产品设计风险。

典型设计构思

Allegro FPS系统中包含多个FPGA芯片库,可以用来协助芯片布局。它可以直接调用Allegro PCB Editor的元件封装来创建floorplan窗口设计,并可以快速创建FPGA系统元件的相对位置。

用户不仅可以通过接口定义来实现FPGA子系统中元件之间的高端连接,还可以创建DDR2、DDR3和PCI

Express等接口定义来实现FPGA与DIMM组件之间或者两个FPGA之间的连接。

此外,Allegro FPGA System Planner 还能够定义配置差分对信号、电源信号和时钟信号。

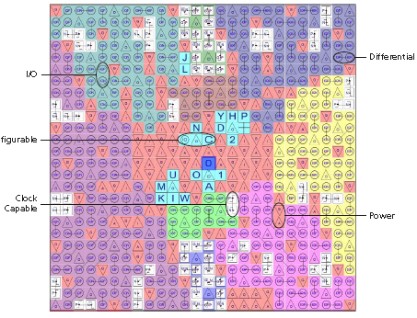

FPGA芯片规则

FPGA System Planner自带多个精确的FPGA芯片模型库,它包括FPGA芯片生产商所确定的引脚配置规则和特殊电气规则。

这些FPGA模型通过合成引擎确保FPGA生产商定义的电气规则被有效执行。这些电气规则,诸如时钟与时钟区域选择、库配置、同步交换预定、缓冲驱动应用以及I/O标准参考电压设定等规则。系统合成过程中,Allegro FPGA System

Planner可以自动检查数以百计的规则组合,用以确保FPGA引脚配置最优化。

合成引脚配置

Allegro FPGA System Planner提供一种基于Allegro

PCB封装的设计方式,用以创建FPGA系统的Placement窗口。用户可以应用DDRx、PCI、SATA、前端总线等接口,实现系统中完成布局的元件与FPGA之间的高端连接,以确保系统中的FPGA与其它元件互连性能,减少FPGA系统设计的构思时间。

一旦确定子系统中FPGA与其它元件连接关系,Allegro FPGA System Planner能够立即按照用户的设计构思,将系统引脚配置、可用FPGA资源、FPGA外围元件布局和FPGA生产商引脚配置规则等进行有效整合。

Allegro

FSP系统内置一个DRC系统合成引擎,可将FPGA生产商提供的引脚配置规则、参考电压规则和终端规则进行有效整合。这种基于规则的合成引擎,可以有效避免多个FPGA连接时PCB设计的反复迭代。Allegro

FPGA System Planner优化了引脚配置算法,可以为一组引脚配置最佳的接口信号,从而能够尽量减少设计中的交叉网络,提高PCB的布线性能。

FSP与Cadence

PCB设计环境紧密集成

Allegro

FPGA System Planner设计平台集成了Design Entry CIS/HDL平台,便于创建FPGA子系统原理图,并且可以调用CIS/HDL元件库中自带的FPGA符号进行原理图设计。如果用户需要,它还可以根据信号连接关系或Bank划分来创建原理图的分割符号库。

FPGA第三方工具数据集成

Allegro

FPGA System Planner不仅与Allegro PCB设计工具紧密集成,还能够与FPGA生产商支持的设计工具实现无缝链接――它可以直接输入和输出FPGA生产商的引脚配置规则文件,这使得FPGA设计师在设计阶段就能够对FPGA引脚的功能配置进行准确评估。

此外,FPGA设计师根据实际功能要求做出的任何设计修改,都可以直接输入Allegro FPGA System Planner工具,从而确保整个设计中引脚功能配置一致。

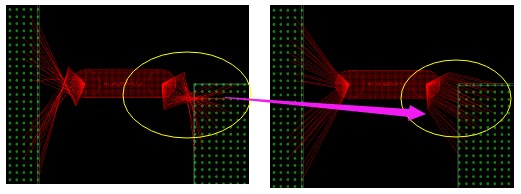

布线前引脚配置优化

初始引脚配置,决定了电路板上FPGA的布局布线性能,然而,减少FPGA设计师、PCB板层设计师、硬件设计师之间的设计迭代还有个很长的过程。

PCB板层设计师规划FPGA相关的接口和信号走线的时候,基于FPGA的走线构思、板层规则和扇出方式的考虑,FPGA引脚配置有可能还需要进一步的优化。

Cadence

Allegro FPGA System Planner当然也考虑到了这一点,它为用户提供了一种优秀的引脚配置的优化方式,允许布局后引脚配置优化,以及FPGA接口、信号线在布线期间的引脚配置优化。

可扩展性

l Allegro FPGA

System Planner ASIC Option,支持4个以上的FPGA的综合管脚分配的并行设计,适用于多个FPGA来做ASIC样品的公司设计

l 4 Allegro FPGA System Planner Option ,可支持4个或少于4个FGPA的综合管脚分配、及后端布局优化设计

l 2 Allegro FPGA System Planner Option,支持2个FPGA的管脚分配和布局后的优化设计

l OrCAD FPGA

System Planner,支持一个FPGA的管脚分配

Cadence FPGA-PCB协同设计解决方案功能对比表格

|

Feature

|

DEMO

|

Allegro 2 FPGA System Planner Option

|

Allegro 4 FPGA System Planner Option

|

Allegro ASIC Prototyping Option

|

|

Max number of FPGAs in a design

|

No limit

|

2

|

4

|

No limit

|

|

Max number of pins with multiple FPGAs

|

No limit

|

2,000

|

4,000

|

No limit

|

|

Define connectivity at Interface level

|

•

|

•

|

•

|

•

|

|

Automatic pin assignment based on rules, con- nectivity

|

•

|

•

|

•

|

•

|

|

Define JTAG chain manually

|

•

|

•

|

•

|

•

|

|

Define PROM chain manually

|

•

|

•

|

•

|

•

|

|

Forward annotation of component placement

|

|

•

|

•

|

•

|

|

Generate symbols and schematics

|

|

•

|

•

|

•

|

|

Export to PDF

|

|

•

|

•

|

•

|

|

Import constraints from Altera, Xilinx, and Actel

|

|

•

|

•

|

•

|

|

Generate PlanAhead and Quartus scripts

|

|

•

|

•

|

•

|

|

Generate OrCAD Capture (symbols, schematics)

|

|

•

|

•

|

•

|

|

Customization through TCL

|

|

•

|

•

|

•

|

|

Group signals from one bank to another

|

|

•

|

•

|

•

|

|

Define terminations in FSP

|

•

|

•

|

•

|

•

|

|

Power mapping

|

•

|

•

|

•

|

•

|

|

HDL port mapping

|

|

•

|

•

|

•

|

|

Use terminators from standard library

|

|

•

|

•

|

•

|

|

Update placement from board file

|

|

•

|

•

|

•

|

|

Create part from Allegro Design Authoring symbol

|

|

•

|

•

|

•

|

|

Generate Allegro Design Authoring (symbols, schematics)

|

|

•

|

•

|

•

|

|

Manual pin swapping in Allegro PCB Editor

|

|

•

|

•

|

•

|

|

Auto generate JTAG chain

|

|

•

|

•

|

•

|

|

Auto generate PROM chain

|

|

•

|

•

|

•

|

|

Virtual interface

|

|

|

•

|

•

|

|

Generic connector

|

|

|

•

|

•

|

|

Swap group of pins within Allegro PCB Editor (FSP as an engine)

|

|

|

•

|

•

|

|

Route Planning (Allegro FPGA System Planner running as an engine in Allegro PCB Editor)

|

|

|

•

|

|

|

Support for 4 FPGAs in a design

|

|

|

•

|

|

|