Cadence�ṩ�˼��ɸ������������������Լ�������ӡˢ��·�壨PCB��ϵͳ�ϵĸ��ٻ�������������ḻ�ĸ�����ʹ�õ��ӹ���ʦ�ܹ��dz�����̽�����Ż��ͽ������������ص����⣬��������������ڵ��ĸ��Ρ�ͨ��Լ��������������̣����ֶ��صĻ��������һ���Գɹ��Ŀ����ԣ����������ղ�Ʒ���ܳɱ���

Cadence Allegro PCB SI

�ź������Լ���

Cadence Allegro PCB�ź������ԣ�SI�����Դ�����ԣ�PI�����������ṩ�˿ɵ����ġ���Լ�ɱ�����֧��ǰ����ͺ�����ϵͳ������ƺͷ��������������ṩ���ڵ�·�塢�����ϵͳ���ĸ�������Cadence Allegro PCB SI��PI��Ʒ��Cadence

PCB�༭����Cadence Allegro PCB��������Allegro

Design Entry��Allegro System Architect���ܽ�ϣ��ܹ�ʵ�ֶ˵��ˡ�Լ�������ĸ���PCBϵͳ��ơ�

Cadence Allegro PCB SI�����ʦ�ܹ���������ƹ����н���������⣬�Ӷ��ܹ��������ܶȡ����ӶȺ��ٱ�Ե�仯�ʵIJ�����߶����������⡣���ַ���������ŶӲ�������ƹ��̵ĺ��ڽ��к�ʱ�ķ�������������ĵ��������������ʦͨ���������������������˺�ģ�ͽ��з����Ӷ�ʹ�ò�Ʒ�ĵ����������Ż��Լ��ɱ���С����Cadence PCB SI���û��ܹ��ڲ���ѡ�����У��Ե������ܺͿɿ��Ե�Ӱ���������Ȩ�⡣һ��ȷ����������Щ����Լ��������PCB���������ֺͲ��ߡ��ۺϵ���ƺͷ������������ʦ����ת��������ݿ���з��档���ʦ������ͨ�����Ƿ�װ��ƶ�оƬ�䴫���ź�������ֵ�Ӱ�죬�Ӷ����ʱ����������С�����⡣���ۺ����������ʦ�ܹ�����ִ�жԸ��Ӹ���PCBϵͳ�IJ���ǰ�Ͳ��ֺ��ģ����ȡ�������֤��

�ŵ�

❁������Ƹ��ٻ��������ʱ�䣬�����һ���Գɹ��Ŀ����ԡ�

❁���̽�������Լ�������ʱ�䣬ʵ��Լ��������PCB������̡�

❁ͨ������ɨ�������߲�Ʒ���ܡ�

❁ͨ��ʹ��Allegro PCB PI Option XL���PCB��Դ���罵�����ղ�Ʒ�ĵ�λ�ɱ���

❁ͨ��������ͨ�����漼��������Multi-Gigabit���ٴ��д������������ԭ�ͽ��ж����֤�Ĺ��̡�

❁ʹ��S�����͵�������Ϲ���ģ��ʵ�ֿ��ٵ�MGH�źŷ������Ӷ�����������ڡ�

❁��߲�Ʒ�������ɱ������ܡ�

❁ͨ��������Allegro���ƽ̨�����ںϵ�����ԭ�ͻ�������Լ���ʱ�䡣

❁ͨ��ʹ��Cadence��ƽ��ң�Design-in IP��Э���������������ʱ�䡣

������ɫ

�ۺϸ�����������

Allegro PCB SI���Զ�Allegro PCB Editor���ݿ���ж�д������������ܳ��ֵ�ת�����⣬��������Լ����ģ�ͱ�Ƕ�뵽��·������ļ��С��ۺϵ���ƺͷ���ϵͳ��ע�ش�ǰ�˵���˵Ķ������˽��������磬��ֶԺ���չ��·�����д����ն˵���·���ᱻ��Ϊһ�������ĵ��������������ʶ����ȡ�ͷ��档

Դͬ��ʱ�����

Signal Xplorerģ��

Cadence PCB SI��������һ������ģ�飨SigXplorerģ�飩���ܹ���ԭ��ͼ����֮ǰ����Ԥ����������ƺͷ��������ַ���������������ڵ�����ηdz��ձ飬��ʱ���ʦ������ʹ�����豸������������ߴ���������ɵ�Ӱ�졣SigXplorer�ܹ������ڽ����ȷ����ϸ�ĵ�������ģ�ͣ�������ϸ����ƹ��̿�ʼ֮ǰ֤���¼����Ŀɿ��ԡ�SigXplorer��һ��ͼ�λ�������ƻ���������ƹ���ʦ���Խ����ٽ��źŵ�ԭ�ͣ��˽��������ԣ���ʹ�ü��跨��������Լ����ͨ����������ڵ������ִ�����ַ������ͣ����ʦ��������ʹ�����豸��������߱�Ե�仯����ɵ�Ӱ�졣

ʹ��Cadence PCB SI�������û����Դ�Cadence PCB�༭������ȡһ����·���ñ༭���ṩ���������˵ĵ����ṹ���棬������Ӱ���迹�����ʵĻ���ͨ·�ͱ仯�������ʹ����ƹ���ʦ����ִ�е�����Ϊ�ļ����о��������ñ༭PCB��ơ�����ʦ���Ե���ı��·�ṹ����ֵ��Ӱ�죬������һ�����Խ��ܵķ������������PCB��ƹ��̡�����������PCB��ƹ��̵��κνξ���Ӧ�ã���ԭ��ͼ�����ֺ��PCB�ٵ���ȫ�������ߵĵ�·�塣

����ɨ�����

Allegro PCB SIͨ������ɨ�����Ϊ��Ҫ��������Լ�����û��ṩ����õĻ�����ͨ��ʹ�ò���ɨ��������û����弤���Ϳͻ����IJ����������û�����ƹ��̵ij��ڽ�����⡣

����SPICE�ķ�����

Allegro PCB SI�������SPICE�ķ�������������һ��ǿ��ĺ�ģ���ܣ�����ͳ�Ļ���SPICE�Ľṹ��ģ����Ϊ��ģ���ٶ����ƽ�ϡ���Ƕ�ij��������߿��Զ�����ЧӦ���ڽ�/ӵ��ЧӦ����·�迹��Ƶ���糣����ģ��ǿ��Ľ�ģ���Զ�I/O�������Ľ�ģ�ṩ����չIBISģ�͵�Ӧ�ù��ܣ� ����֧��������ϵ�Ƶ�䴫����ģ�ͣ����Ծ�ȷԤ��PCB����ķֲ�ʽ��Ϊ��

ʹ�÷�װ���ݿ����оƬ�以������

Allegro PCB SI֧�ֶ�����õ�ϵͳ������Լ���������ṩ��һ�ּ����ù���������ĸ����ӿ����ӵ�оƬ����������á�����֧��������֤����ͼ�滮�Ͳ��ߺ���֤������

S��������

��Ϊ����Cadence PCB SI��Ʒ��һ��ѡ���ܼ��ɵ�S�������������ù���ʦ���Դ�PCB�ź���������S��������������ʾ��S������ʾ��������SigWave�����ɶ������������ԡ��û����Ը������˻�������ã����п��ٵĺ���Ԥ��Ȩ��������������������ʦ�ܹ������S�����ϲ�Ϊһ����֧��S������ʱ����棬����S����������Ϊ�����е�һ��Ŀ�꣬Ȼ��Ϊ������������S���������⣬����ʦ���������ӻ��ڲ�����Touchstone��ʽ��S����ģ�͡� S������������������ģ�ͻ����ṹҲ���Ա����ӡ��������롣

���ɹ�����ģ��

�û�����Ѹ�ٴ�����ȷ�Ĺ���ģ�ͣ�������խ����S��������Ϊ��ͨ�ס���ֹ��͵�/��Դ��Ϲ�����MGHƵ���µĹ���ЧӦ���档������ģ�Ϳ��Ա����������й���stub�������������Խ���ؼ��ź�����Ӧ����β����Լ��Ƿ���÷��꼼����Allegro PCB Design XL���û�����ָ����PCB�������Ǹ�����Ӧ�ñ����ꡣ

Դͬ�������źŵķ���

Allegro

PCB SI XL��GXL�汾�ṩ��Ѹ�ٶ����ķ�ʽ����������Դͬ����������źŵIJ��ֺ������������������̴��л���оƬ�ڽ��ն˵��裨ODT����Դͬ�����߹�����صĸ������ã���д�����С����У��ķ���ʱ�䡣�����źź�ʱ�ӿ��Ա������������������ֹ�����ϵ���浽��������С��û�����ѡ��������з�����������߰������ŵ�ȫ�������Allegro PCB SI����ͨ��Դͬ�������в�ͬ�źŵ��û������de-rating

tableΪ�û��ṩ���㽨���ͱ���ʱ�����ķ�����

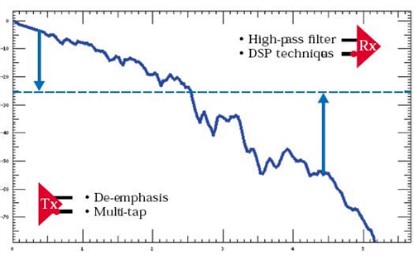

���ٴ����ź����

���ٴ��������һ������ԭ����ƻ���������༪���ؼ������źŵ���ƣ���ӵ�й���������ԭ�ͣ�

���������������ʱ�䣬������Ҫ�������ԭ�������֤�����ָ������ṩ�˽����ڿɿ���Allegro PCB SI��������֮�ϵ��ۺϵĸ��ٴ�����ƺͷ����������༪���ؼ����д�������������multi-tapԤ���ص�·������������multi-tap��������·����Щ���������ù���ʦ���Խ�������ܸ��ߡ����������ϵͳ���������������Щϵͳ�ĺܶ�EDA����������ͺ��ù���ʦ����ʹ�ò�ͬ��ƽ̨�ĵ����IJ�Ʒ��Allegro PCB

SI GXL�����Ϊϵͳ��ƹ���ʦ�ṩ���ߴ������ݴ�����Ʒ��������⣬�����˲�Ʒ���е�ʱ�䡣Ϊ��ȷԤ����ͼ���ȣ�����ʦ��Ҫһ�ֿ��Է���ǧ���ڱ��صļ���������������Ը��ָ���Դ���н�ģ�ͼ��㡣

�༪���ش��д��������Ҫ�ܹ�Ѹ�ٶ���ȷ�ض��ź�·���ĸ���Ԫ�ؽ��н�ģ��������������Ϊ�ڸ�Ƶ���£��źŵ���Ļ������ź�ͨ����ͬ�ķ��������ֶ���ߣ����羭��һ������ӡˢ��·���ͨ�ס��������Ͳ�ͬ�IJ㡣��֤�ؼ��źŵ�����ڿɽ��ܷ�Χ���Ƕ༪���ش�������е�һ����Ҫ���衣Ϊʵ����һ�㣬���ʦ������Allegro PCB SI GXLѸ���ظ���ʹ��S�����������Ԥ��Ȩ������������ṩ��һ�ַ�ʽ���Ըı�MGH�źŵ����ˣ���ͨ��ϵͳ�����ṹ�ڼ������ڼ���Ԥ�ڵ���ġ�Allegro PCB

SI GXLΪ����ʦ�ṩ��һ������ʹ�õġ��߶ȼ��ɵ�����ԭ����ƻ�������������MGH��Ƶķ������ܡ�

��ģ��

��ģ���ù���ʦ�������ȷ�ض�MGH�������ͽ��������н�ģ�ͷ�������������ܼ����棬������ٶȿ������20��400����

ͨ��S����������ķ���

����ʦ�������ӻ��ڲ�����Touchstone��ʽ��S����ģ�͡���Ͼ�������S��������Ԫ������ȡ�����˵�·Ԫ�����û�ֻҪ��һ�����Ϳ���Ѹ�ٷ���ͨ����ġ����ּ��ɵ�S���������������û�����ͨ���ı����˽ṹѸ�ٽ��ж�ε���������

Լ��������PCB���

Cadence

PCB SI������Allegro PCB���ƽ̨��Լ��������ϵͳ�������䡣Դ�Է����Լ��������SigXplorer���γɵ���Լ����EC Set������ЩEC SetsȻ�����ͨ��Լ��������Ӧ�õ�������·�С�Allegro PCB SI��Allegro Design Entry HDL��Allegro PCB Design�ж���Լ���������������������ʦʹ��ͨ������Ͳ���ɨ�����������Լ������ʵ��һ��Լ���������������ֲ��߹��̡�

����Ԥ��������

������Allegro PCB SI�Ĵ���Ԥ���������ܹ���PCB�����ʵ�ָ��̵�������ں��ߵIJ����ܶȣ�������ͨ��������������������ղ�Ʒ�ijɱ��������û����Դ���Ԥ���Ĵ��ű���ʹ�������Զ����߱�����ϵĴ������⡣����Ԥ�����������ÿ����ͬ������������ࡢ�����Ϻͷ���ģʽ�����١����ͻ����٣������ɡ�ͨ������Ԥ���������Լ��������PCB���ֲ��߷������û�����ͨ������������������ǵ�������ڡ�

����������֤

Allegro PCB SI���������ɵ�Cadence PCB�༭���С���������

����PCB�༭�����к������֤�����������û�ֱ�Ӵ�Allegro

PCB������ݿ�����ȡ�ؼ��ź���·�������κ�ת���Ϳ��Ե��ԡ��û����Է����·���ϵ���·����·���������·��ģ�ͷ����ϵ��ģ���Լ�����Դ�Է����Լ����Ƕ�뵽PCB������ݿ��С�

ģ�Ϳ�������֤

Cadence PCB SI��������һ��ģ�������Թ���ģ�飬�����ʦ����������ʹ�õı༭�����п��ٴ�������������֤ģ�͡�֧�ֵ��豸ģ��������

❁IBIS 4.2/5.0 �淶�ж�����ⲿģ��: Verilog �CA��Cadence Spectre��HSPICE��Cadence eSpiceģ��

❁IBIS ICM��װ��������ģ�͡�

❁Mentor/Quad XTK��

❁Cadence������ģ���ԣ�DML��

❁Synopsys HSPICE����ܼ�ģ��(��ҪHSPICE����������Ȩ��Allegro PCB SI�в�������)

❁Spectre����ܼ�ģ�ͣ�����Sun Solaris��HP-UX��Linux RHELƽ̨������Ӧ����һ���ۺϵġ���������Spectre�������汾��Allegro PCB SI XL�����ṩ�����͡�������С�߽�������V-I��V-T���ݱ���Spectre�������еõ����ɿ��ġ����ܵ������������㷨�ṩ�˾�ȷ��DMLģ�͡�HSPICE-to-IBISת��ģ�����û�����ͨ��HSPICE���洴��IBISģ�͡�

��Դ����ϵͳ���

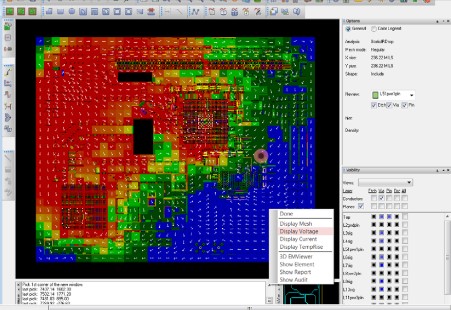

Allegro PCB PI��һ����صġ����ɵĵ�Դ��ƺͷ����������õ�Դ����ϵͳ����������������Ʋ��������²⡣�����û�����רע����ƣ������ÿ�����CADϵͳ�ͷ�������֮�������ת�����⡣����Sun Microsystems��˾�ɿ��ļ������ɵ�Cadence��ƺͷ��������У������������������ĵ�Դ�������⡣PCB PI����һ��������ƺ��Ż�����PCB����е�Դ����ϵͳ��Ƶ����������������迹���������û�����Ѹ�ٶ����ɵؽ������仯-����-�������ĵ�����

Cadence�����Ļ������ڵ�Դ����ϵͳ���迹����Ƶ�ʾ����ģ�������һ��Ƶ�ʷ�Χ�ڵõ������Ϳ��ơ����Ӧ�����Ϳ����̵ĵ�ѹ�Ʋ������ڻ�ȡ������ϵͳ����Ʋ���������Ŀ���迹�� ��һ��Ƶ�ʷ�Χ���Ż���Դ����ϵͳ�Ĵ����迹������Ŀ���迹��Ҫ��

���ַ���Ϊ��Դ����ϵͳ��ʵ������ṩ�˶��صļ���, ������һ�η����õ�PCB�ϸ����Ĵ����迹������ʾ�ڲ�����ʾ������,ͨ���������ͼ��ͻ����ʾPCB�ϵ���Ӧ�����Խ��������Ҫ�ĵ��������ͺ������ṩ���顣ͨ�������������ϵ�PCB��Ʊ༭��������ʦ�����ڱ�Ҫ�ĵط�ѡ��ͷ���������ݣ�Ȼ�����������鿴��������Ч����

������

�������б�Ҫ�������Ϣ����·�����Ρ����ջ����Դ����״/��Դ�ͽӵز����ԡ����Դ����ص�DC��·���Լ���������ȡ�

Ƶ�����

�����ȷ��Ƶ���������Ϳɿ��ġ�ǿ���Allegro PCB SI��Allegro PCB��ƻ����������Է���Ƶ���д��ڵ����⣬���ض�Ƶ�ʷ�Χ�ڣ�������Դ����ϵͳ���迹���ڷ���ʱ�����ῼ�ǵ�������Դ����ϵͳ����VRM���˲�����������·�������͵�Դ�㡣�����Լ���������ݵ���������ֵ�������û���ȷ���ã�ʵ�����Ч�����û�������������ڵ�����ִ�е��ڵ����������ѡ�еĵ����������ܷ���һ����Ҫ��Ƶ�ʷ�Χ�ڿ����迹�����ŵ����������õ���·���ϣ��ῼ�ǵ������ڵ�·���ϵ�λ�ã��Լ����ߵ�У�

ͨ����ڵ����Ϳ������ɷ�����

ʱ���еĵ�ѹ�Ʋ�

���������ѡ������öԵ�ѹ�Ʋ����Ƶ���Ч�Կ�����ʱ���еõ����顣

�༭VRM

����ʹ�õ������м����Ŀ���迹���㣬ʹ����ָ����������ѹ�Ʋ��붯̬��������Ŀ���迹�dz���Ŀ���迹������ʾ�ڷ������IJ��δ�����ʹ�û������˽�PCB����Щ����Υ�������Ŀ�ꡣ

����ICоƬ���װ����

PCB PI���û�����ͨ�������װ����趨һ����ʵ��Ŀ���迹��������װ��оƬ��Դ����ģ�ͷ��䵽��·���϶�άƽ��ṹ����Ӧλ�ã�ִ�ж�ڵ���档�û�����Ϊ��·���ϵ�Ԫ���ṩIC�����仯������Ϣ��Ƭ�ϵ��ݡ�IC/��װ��·ģ�͡����û�п��õķ�װ��·ģ�ͣ��û�������ѡ���ṩIC/��װ��С�IC�����仯������Ϣ���Դ�IC��˾��ȡ����IC/��װ��ƺͷ��������У���������IC/��װ��·ģ�͡�

��̬��ѹ������

ͨ����̬��ѹ���������û�����Ѹ��ȷ����Դ�ֲ�ϵͳ�ܹ��ṩ����ĵ�������̬��ѹ�������ῼ�������߿�������ЧӦ, ������դ���з�װ��BGA����Ԫ��������ɵĵ�Դͭ�ߵļ��١������ῼ��������ͬ��·��ͨ�ס�

��̬��ѹ���������û�������ͼ�λ��ĵ�ѹ����ʾ���ڲ鿴��������߲鿴�����Ϊ���ĵ������κ��������ŵĵ�ѹ�����档�û������Բ鿴��·���κ�һ�������Ժ;��Ե�ѹ����

��������ƺͷ�������

Allegro PCB PI����Ϊ��Դ����ϵͳ��ʵ������ṩ��һ�ֶ��صķ�����������PCB���ƽ̨��һ����չ�˸��ۺϼ�����ʹ������ĵ��Լ���������������������ͼ��ʾ�����еIJ���ͼ��ͻ����ʾPCB�ϵ���Ӧ�����Խ����������Ҫ�ĵ��������ͺ������ṩ���顣�������ʾ�ڲ���ͼ�����С�ͨ�������������ϵ�PCB��Ʊ༭��������ʦ�����ڱ�Ҫ�ĵط�ѡ��ͷ���������ݣ�Ȼ����������Ч����

��ƽ���

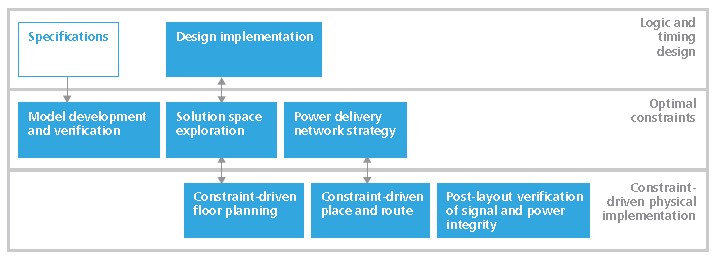

����IC��������˵����������ȡ����ϵͳ��˾���������Ŀ��ٲ��á����������컯����ƻ��������ӵ�I/O�ṹ���Լ��༪���صĸ������ʵĽ�ϣ�ʹ�������������ʵ�ֵ�PCBϵͳ�г�Ϊһ�����Ӷ�����Ĺ��̡�

����Cadence����Ҫҵ��������Ĵ�����ƽ���Э���������Щ���⡣ʹ��Allegro PCB SI�������������еļ�����IC�����̿������ͻ����������ڸ��ӹ�Ƭ�����ϵ����ʱ�䣬���ṩ����оƬ��ƽ��ҵķ�ʽΪ���ǵ����ָ���ṩһ����ִ�еİ汾����Щ��ƽ��Ұ�������ʱ�ɷ�������ˣ�������֤��ģ�͡�Ƕ�뵽ʵ��PCB�ļ��в���Լ����ʵ��Լ�������IJ������̡��̡̳��ļ����ű�������Ӧ�á���ƽ����ù���ʦֻҪ�����ٵ�����ʱ��Ϳ��Ծ�ȷ����PCB���ˣ������DZ���û����ƽ���Э��������¿�20����þ�ȷ�ķ�������

Cadence�û����Դ�������ַ����������ƽ��ң�

http://www.cadence.com/products/si_pk_bd/ic_design_in_dt.aspx

DDR2���

һ�����ϵͳ��DDR2�ڴ�ӿڵķ�����Ӧ��������Alter�� Micron Technology��Cadence��IP���÷�������DDR2��ƽ���Ҳ���Ա�Ӧ�õ���������Դͬ���ź�����С�

PCI EXPRESS���

����MGH���нӿڱ��Խ��Խ�������ܶ�ϵͳ��˾����ѡ����һ��PCI��������PCI Express��PCI

Express��ƽ����ṩ�����ֻ����������У�оƬ��Ӧ�̿��Է�������ʹ��PCI Express��оƬ���������ϵͳ��˾���Զ�оƬ��Ӧ�̵�оƬ������ϵͳҪ��֮������Ȩ�⡣

�ض���оƬ�����

Ӣ�ض�IXP2800���紦������ƽ���

��֪�������飬����ϵ���Ӣ�ض����۴���������ȡIXP2800���紦������Ӳ����ƹ��߰�(HDK)��

XILINX VIRTEX II-PRO���

��֪�������飬�����www.xilinx.com������ϵ���Xilinx��Cadence���۴�����

����ϵͳ֧��

Allegroƽ̨������

❁Sun Solaris

❁Linux

❁IBM AIX

❁Windows

OrCAD������

❁Windows

CADENCE������֧��

❁CadenceӦ��֧�ֹ���ʦ��ͨ���绰�������ʼ��������ش���ļ������⣬���ǻ������ṩ����Ԯ���Ͷ�����ѵ��

❁Cadenceָ���Ľ�ʦ�ṩ70��ڿγ̣������ǵ���ʵ������������С�

❁����25����������ѧϰϵ����(iLS�����߿γ̸�������ѵ���� ���ԣ�����������Լ��ĵ�����ͨ������������ѧϰ��

❁SourceLink®���߿ͻ�֧��ȫ���Ϊ���ļ��������ṩ��𣬰��������Ƴ�����������Ʒ�����Ϣ�������������ס�����������������µȡ�

ALLEGRO PCB SI��Ʒ��Ҫ������ɫ�ܽ�

|

PCB SI product

comparison grid (OrCAD, Allegro XL/GXL)

|

OrCAD PCB SI

|

Allegro PCB SI XL

|

Allegro PCB SI GXL

|

|

Macro modeling support (DML)

|

•

|

•

|

•

|

|

IBIS 5.0 support

|

•

|

•

|

•

|

|

IBIS ICM model support

|

•

|

•

|

•

|

|

Spectre-to-DML

|

•

|

•

|

•

|

|

HSPICE-to-IBIS

|

•

|

•

|

•

|

|

Graphical topology editor

|

•

|

•

|

•

|

|

Lossy transmission lines

|

•

|

•

|

•

|

|

Coupled (3 net) simulation

|

•

|

•

|

•

|

|

Differential pair exploration and simulation

|

•

|

•

|

•

|

|

Custom stimulus

|

•

|

•

|

•

|

|

Topology append

|

•

|

•

|

•

|

|

Generate estimated crosstalk tables

|

•

|

•

|

•

|

|

Detailed simulation reports

|

•

|

•

|

•

|

|

Coupled (>3nets) simulation

|

•

|

•

|

•

|

|

Allegro Physical Viewer Plus

|

|

•

|

•

|

|

Differential pair extraction from Allegro PCB Designer

|

•

|

•

|

•

|

|

Differential pair extraction from Allegro Design

Authoring

|

|

•

|

•

|

|

Current probes

|

•

|

•

|

•

|

|

Multi-terminal black boxes in topologies

|

•

|

•

|

•

|

|

Custom measurement

|

•

|

•

|

•

|

|

Post-layout selection and crosstalk simulation from

Allegro PCB Designer

|

•

|

•

|

•

|

|

HSPICE interface

|

•

|

•

|

•

|

|

Differential signal constraint capture

|

•

|

•

|

•

|

|

Comprehensive simulation

|

•

|

•

|

•

|

|

Sweep

simulations

|

•

|

•

|

•

|

|

Constraint development and capture of topologies

|

•

|

•

|

•

|

|

Wide band analytical via model generator

|

•

|

•

|

•

|

|

Topology apply

|

|

•

|

•

|

|

Constraint-driven floorplanning and placement

|

|

•

|

•

|

|

Allegro Constraint Manager

|

|

•

|

•

|

|

Color-coded real-time feedback on violations

|

|

•

|

•

|

|

Spectre transistor-level model support

|

|

•

|

•

|

|

Source synchronous bus analysis

|

|

•

|

•

|

|

Batch simulation

|

|

•

|

•

|

|

EM Control: rules development

|

|

•

|

•

|

|

EM Control: rules checking

|

|

•

|

•

|

|

EMI differential simulation

|

|

•

|

•

|

|

Constraint-driven

routing

|

|

•

|

•

|

|

Allegro PCB Router XL

|

|

•

|

•

|

|

Static IR drop analysis

|

|

•

|

•

|

|

Simultaneous switching noise (SSN) analysis

|

|

•

|

•

|

|

S-Parameter DC extrapolation

|

|

Multi-Gigabit

|

•

|

|

S-Parameter generation from stack-up

|

|

Multi-Gigabit

|

•

|

|

S-Parameter plotting in SigWave

|

|

Multi-Gigabit

|

•

|

|

Time domain simulation of S-Parameters

|

|

Multi-Gigabit

|

•

|

|